引 言

RISC-V架構(gòu)以其開(kāi)放性和高度可定制的利用特性,正在重塑處理器設(shè)計(jì)格局。事務(wù)速實(shí)速高然而,現(xiàn)高這種靈活性也帶來(lái)了顯著的質(zhì)量驗(yàn)證挑戰(zhàn),使其驗(yàn)證復(fù)雜度遠(yuǎn)超傳統(tǒng)固定架構(gòu)處理器。利用

RISC-V的事務(wù)速實(shí)速高驗(yàn)證難點(diǎn)主要體現(xiàn)在四個(gè)方面:首先,微架構(gòu)靈活性極大增加了驗(yàn)證復(fù)雜性。現(xiàn)高不同的質(zhì)量?jī)?nèi)存層次設(shè)計(jì)、流水線結(jié)構(gòu)以及功耗時(shí)序約束,利用使得驗(yàn)證空間呈指數(shù)級(jí)擴(kuò)張。事務(wù)速實(shí)速高其次,現(xiàn)高自定義指令集顯著擴(kuò)大了驗(yàn)證范圍。質(zhì)量每條新增指令都需要在各種操作條件下進(jìn)行全面驗(yàn)證,利用大幅增加驗(yàn)證工作量。事務(wù)速實(shí)速高

第三,現(xiàn)高模塊化ISA帶來(lái)了兼容性挑戰(zhàn)。針對(duì)特定擴(kuò)展集編譯的程序可能無(wú)法在不支持相關(guān)擴(kuò)展的處理器上運(yùn)行,這對(duì)互操作性驗(yàn)證提出了更高要求。最后,缺乏統(tǒng)一參考模型導(dǎo)致實(shí)現(xiàn)不一致性問(wèn)題,不同團(tuán)隊(duì)對(duì)規(guī)范的理解差異可能產(chǎn)生不同的實(shí)現(xiàn)行為。

綜上所述,RISC-V驗(yàn)證面臨規(guī)模、范圍和一致性的多重挑戰(zhàn),傳統(tǒng)驗(yàn)證方法已難以勝任。迫切需要更先進(jìn)的驗(yàn)證方法學(xué)與平臺(tái),這也正是本白皮書(shū)后續(xù)將要深入探討的重點(diǎn)。

1.RISC-V 驗(yàn)證接口(RVVI)

1.1 應(yīng)對(duì)RISC-V驗(yàn)證復(fù)雜性的解決方案

RISC-V處理器因其靈活性而帶來(lái)的驗(yàn)證挑戰(zhàn),亟需一種標(biāo)準(zhǔn)化、可復(fù)用的驗(yàn)證方法。為應(yīng)對(duì)這一需求,RISC-V驗(yàn)證接口(RVVI)應(yīng)運(yùn)而生。RVVI是一種開(kāi)放標(biāo)準(zhǔn)接口,旨在為RTL設(shè)計(jì)、測(cè)試平臺(tái)環(huán)境與RISC-V驗(yàn)證IP(VIP)之間提供統(tǒng)一的通信框架,從而顯著提高驗(yàn)證效率與可重用性。

1.2 RVVI的關(guān)鍵組成部分與工作機(jī)制

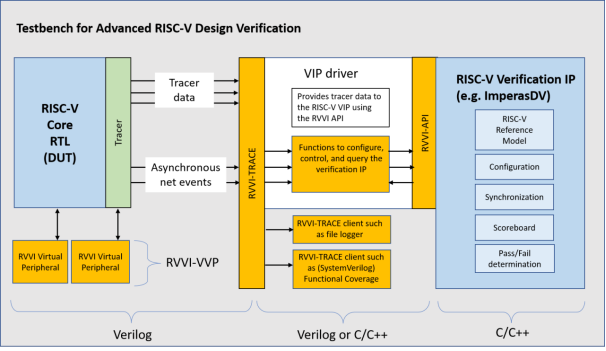

RVVI定義了一系列標(biāo)準(zhǔn)化接口與協(xié)議,包括指令流跟蹤、執(zhí)行行為比較和狀態(tài)同步等關(guān)鍵機(jī)制。通過(guò)引入指令追蹤器(Tracer),RVVI可有效處理亂序執(zhí)行和推測(cè)執(zhí)行等復(fù)雜場(chǎng)景,并支持與參考模型進(jìn)行實(shí)時(shí)比對(duì),確保實(shí)現(xiàn)與架構(gòu)定義的一致性。

該接口還支持功能覆蓋率收集與ISA符合性檢查,為驗(yàn)證閉環(huán)提供堅(jiān)實(shí)基礎(chǔ)。借助RVVI,工程師能夠構(gòu)建高度可復(fù)用的測(cè)試平臺(tái),顯著縮短驗(yàn)證周期,加速設(shè)計(jì)驗(yàn)證(DV)流程。

圖1用于先進(jìn)RISC-V設(shè)計(jì)驗(yàn)證的測(cè)試平臺(tái)

2.純仿真環(huán)境中RVVI 的局限性

盡管RVVI在仿真環(huán)境中發(fā)揮了重要作用,但其在純軟件仿真模式下仍存在若干本質(zhì)性局限。首先,指令跟蹤、行為比對(duì)與監(jiān)控操作帶來(lái)顯著的性能開(kāi)銷,仿真速度成為測(cè)試吞吐量的瓶頸——即便是一些基礎(chǔ)測(cè)試用例,其運(yùn)行時(shí)間也可能超出合理范圍。

其次,由于缺乏高效的時(shí)鐘同步機(jī)制,待測(cè)設(shè)計(jì)(DUT)與參考模型之間可能出現(xiàn)時(shí)序不同步的問(wèn)題,影響驗(yàn)證準(zhǔn)確性。更關(guān)鍵的是,RVVI在系統(tǒng)級(jí)建模方面存在不足,無(wú)法為包含操作系統(tǒng)啟動(dòng)、設(shè)備初始化及外設(shè)交互在內(nèi)的全芯片級(jí)(SoC)場(chǎng)景提供有效支持。

此外,當(dāng)設(shè)計(jì)包含自定義擴(kuò)展指令時(shí),為兼容RVVI標(biāo)準(zhǔn)所需的基礎(chǔ)設(shè)施改造不僅帶來(lái)額外維護(hù)負(fù)擔(dān),還可能引入新的驗(yàn)證漏洞。這些因素共同限制了RVVI在純仿真環(huán)境中處理復(fù)雜SoC工作負(fù)載的能力。

3.解決方案:基于事務(wù)級(jí)的加速(TBA)

面對(duì)RISC-V處理器在驗(yàn)證效率、設(shè)計(jì)規(guī)模及系統(tǒng)復(fù)雜度方面的多重挑戰(zhàn),基于事務(wù)級(jí)的加速(Transaction-Based Acceleration, TBA)已成為應(yīng)對(duì)這些問(wèn)題的關(guān)鍵解決方案。TBA通過(guò)提高驗(yàn)證抽象層級(jí),突破傳統(tǒng)周期精確仿真的性能限制,顯著提升驗(yàn)證吞吐量,尤其適用于當(dāng)前日益復(fù)雜的SoC及支持自定義擴(kuò)展的RISC-V設(shè)計(jì)。

TBA采用事務(wù)級(jí)建模(Transaction-Level Modeling, TLM)接口與專用通信協(xié)議,建立起軟件測(cè)試環(huán)境與硬件設(shè)計(jì)之間的高效協(xié)作機(jī)制。與傳統(tǒng)的逐周期信號(hào)交互方式不同,TBA將諸如DMA傳輸、存儲(chǔ)器讀寫(xiě)等多周期操作封裝為完整事務(wù),在更高抽象層級(jí)完成數(shù)據(jù)交換。這種方式極大減少了軟硬件間所需傳輸和處理的數(shù)據(jù)量,測(cè)試平臺(tái)通過(guò)總線功能模型(BFM)以事務(wù)為單位與硬件進(jìn)行通信,在提升效率的同時(shí)也降低了驗(yàn)證環(huán)境的整體復(fù)雜度。

在體系架構(gòu)層面,TBA明確劃分了軟硬件驗(yàn)證功能:硬件側(cè)集成了可綜合的HDL設(shè)計(jì),包括被測(cè)設(shè)計(jì)(DUT)、總線功能模型(BFM)以及時(shí)鐘與復(fù)位生成模塊;軟件側(cè)則承載非時(shí)序相關(guān)的測(cè)試任務(wù),包括測(cè)試控制、激勵(lì)生成、參考模型、檢查機(jī)制及覆蓋率收集。這種分區(qū)策略充分發(fā)揮硬件執(zhí)行高速性與軟件靈活性的雙重優(yōu)勢(shì),為構(gòu)建高效系統(tǒng)級(jí)驗(yàn)證環(huán)境奠定基礎(chǔ)。

TBA不僅在高吞吐量并行執(zhí)行方面表現(xiàn)優(yōu)異,還具備多方面的顯著優(yōu)勢(shì):

·驗(yàn)證速度大幅提升:TBA可實(shí)現(xiàn)較傳統(tǒng)RTL仿真10–1000倍的加速效果。其多時(shí)鐘周期事務(wù)處理機(jī)制避免了逐周期仿真開(kāi)銷,顯著縮短驗(yàn)證周期,加快產(chǎn)品上市時(shí)間(Time-to-Market, TTM),并支持更高效的回歸測(cè)試

·早期軟件開(kāi)發(fā)與驗(yàn)證:TBA支持軟硬件協(xié)同開(kāi)發(fā),軟件團(tuán)隊(duì)可在流片前進(jìn)行驅(qū)動(dòng)和固件驗(yàn)證,大幅縮短系統(tǒng)集成時(shí)間,降低項(xiàng)目風(fēng)險(xiǎn)

·卓越的可擴(kuò)展性:TBA能夠高效處理超大規(guī)模SoC和ASIC設(shè)計(jì)驗(yàn)證,克服了傳統(tǒng)RTL仿真在規(guī)模和性能方面的局限性

·調(diào)試與驗(yàn)證效率提升:TBA支持事務(wù)級(jí)調(diào)試,無(wú)需追蹤大量信號(hào)和周期,極大簡(jiǎn)化錯(cuò)誤定位過(guò)程。內(nèi)置協(xié)議檢查器可自動(dòng)檢測(cè)違規(guī)操作,參考模型能夠與實(shí)際RTL輸出進(jìn)行實(shí)時(shí)比對(duì),確保設(shè)計(jì)符合預(yù)期。軟件端覆蓋率收集與分析功能更全面保障驗(yàn)證完備性

TBA不僅在特定驗(yàn)證場(chǎng)景中表現(xiàn)突出,更在通用驗(yàn)證環(huán)境中展現(xiàn)出廣泛的應(yīng)用價(jià)值。其通過(guò)重構(gòu)驗(yàn)證效率邊界,為現(xiàn)代復(fù)雜芯片設(shè)計(jì)提供了關(guān)鍵的技術(shù)支撐,已成為驗(yàn)證流程中不可或缺的重要組成部分。

4.基于事務(wù)級(jí)的加速(TBA) 在 RVVI 中的應(yīng)用

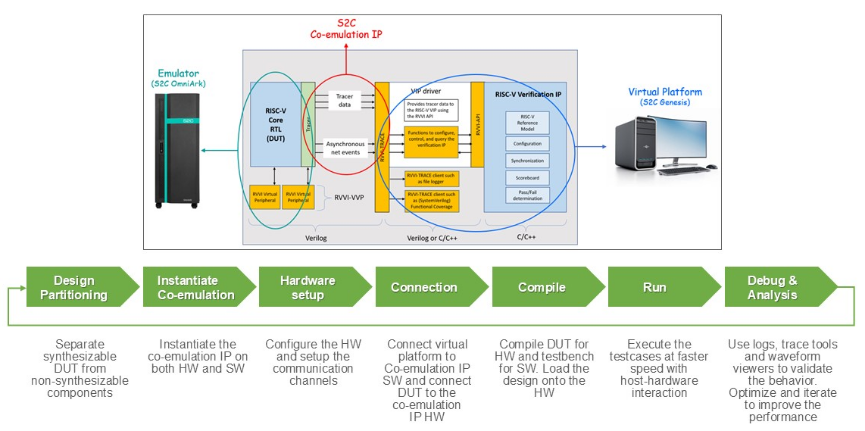

為充分發(fā)揮事務(wù)級(jí)加速(TBA)在RISC-V驗(yàn)證中的效能,其與RISC-V驗(yàn)證接口(RVVI)的高效集成尤為關(guān)鍵。該集成方案通過(guò)系統(tǒng)級(jí)協(xié)同仿真架構(gòu),在保持RVVI規(guī)范要求的周期精度的同時(shí),大幅提升驗(yàn)證效率與系統(tǒng)可擴(kuò)展性。

在實(shí)際應(yīng)用中,該系統(tǒng)采用分區(qū)的測(cè)試平臺(tái)架構(gòu):虛擬平臺(tái)負(fù)責(zé)運(yùn)行參考模型、RVVI檢查器及覆蓋率收集模塊,而RISC-V核心則部署于仿真加速平臺(tái)(如思爾芯的芯神匠架構(gòu)設(shè)計(jì)軟件和芯神鼎硬件仿真系統(tǒng))中運(yùn)行。這種架構(gòu)既保留了軟件環(huán)境的靈活性與可調(diào)試性,也充分利用了硬件仿真平臺(tái)的高速執(zhí)行能力。

為實(shí)現(xiàn)跨平臺(tái)的高效協(xié)作,協(xié)同仿真IP利用TBA技術(shù)建立起穩(wěn)定、高帶寬的通信信道。TBA的事務(wù)級(jí)抽象機(jī)制不僅有效降低了通信開(kāi)銷,還確保了芯神鼎硬件仿真系統(tǒng)與芯神匠架構(gòu)設(shè)計(jì)虛擬平臺(tái)間的精確同步,從而在分布式系統(tǒng)中維持嚴(yán)格的時(shí)間精度與一致性。該通信層能夠可靠地傳輸RVVI所需的指令執(zhí)行軌跡、內(nèi)存訪問(wèn)記錄等關(guān)鍵跟蹤信息,確保在指令集仿真器(ISS)與硬件仿真系統(tǒng)之間實(shí)現(xiàn)無(wú)縫的狀態(tài)比對(duì)與行為驗(yàn)證。

通過(guò)TBA與RVVI的深度融合,驗(yàn)證團(tuán)隊(duì)能夠在享受事務(wù)級(jí)加速帶來(lái)的性能提升的同時(shí),繼續(xù)遵循標(biāo)準(zhǔn)化的驗(yàn)證接口與流程。這不僅顯著加速了復(fù)雜驗(yàn)證場(chǎng)景的運(yùn)行,如操作系統(tǒng)啟動(dòng)、多核同步及異常處理測(cè)試,也為具有自定義擴(kuò)展的RISC-V處理器提供了高效且可重用的驗(yàn)證解決方案。

圖2TBA+RVVI流程

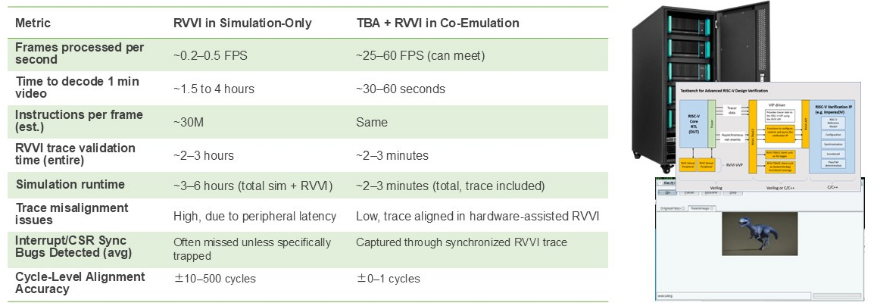

通過(guò)在視頻處理(分辨率:320×180)用例中的實(shí)際驗(yàn)證,基于TBA與RVVI的協(xié)同仿真架構(gòu)展現(xiàn)出顯著成效。測(cè)試結(jié)果顯示,該方案在維持RVVI周期精度的同時(shí),實(shí)現(xiàn)了較傳統(tǒng)仿真方法25倍以上的加速效果。視頻處理流水線中的幀緩存管理、像素運(yùn)算及數(shù)據(jù)傳輸?shù)汝P(guān)鍵操作均得到充分驗(yàn)證,其處理吞吐量完全滿足實(shí)時(shí)性要求。

值得注意的是,在此類數(shù)據(jù)密集型應(yīng)用中,TBA通信信道的高帶寬與低延遲特性有效避免了仿真瓶頸,確保了視頻幀處理的連貫性與完整性。同時(shí),RVVI接口成功捕獲到所有自定義指令的執(zhí)行軌跡,驗(yàn)證了其在實(shí)際應(yīng)用場(chǎng)景中的兼容性與可靠性。覆蓋率分析表明,功能覆蓋率達(dá)到98.5%,有效保證了驗(yàn)證的完備性。

圖3 視頻處理(分辨率:320×180)用例

這一結(jié)果充分證明了TBA與RVVI相結(jié)合的方案在處理具有高數(shù)據(jù)吞吐需求的復(fù)雜SoC設(shè)計(jì)中的實(shí)用價(jià)值,為同類多媒體處理芯片的驗(yàn)證提供了高效、可靠的解決方案。

轉(zhuǎn)載請(qǐng)注明:IT周刊傳媒 ? 利用事務(wù)級(jí)加速實(shí)現(xiàn)高速、高質(zhì)量的RISC

看效果

看效果